# ПОЛУПРОВОДНИКОВАЯ МИКРОЭЛЕКТРОНИКА – 2020.

## ЧАСТЬ 3. МАРАФОНСКАЯ ПОЛУПРОВОДНИКОВАЯ ГОНКА К 1 нм

**ДМИТРИЙ БОДНАРЬ**, к. т. н., генеральный директор, АО «Синтез Микроэлектроника»

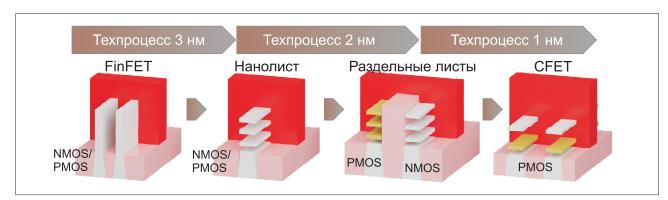

Эпоха применения архитектуры FinFET транзисторов в современных сверхсложных интегральных микросхемах завершится на 3-нм технологии. На смену им приходят транзисторы GAAFET с круговым затвором. Противостояние между TSMC и Samsung в освоении новых технологий обещает серьезную конкурентную борьбу между этими компаниями за мировой контрактный рынок. Отстающая Intel декларирует освоение 1,4-нм процесса к 2029 г. Достижение рубежа 1 нм не за горами, несмотря на гигантскую стоимость разработки, освоения новых технологий и появление серьезных технических проблем.

#### **ЭВОЛЮЦИЯ**

### от 10 мкм к 1 мкм и 1 нм

История интегральной микроэлектроники насчитывает около 60 лет и является примером поступательной технической эволюции, не прекращавшейся никогда за все эти годы даже в периоды неоднократных мировых экономических кризисов. Но если переход от первой интегральной схемы на технологию с психологическим барьером в 1 мкм занял около 24 лет (см. табл. 1), то дистанция от 1 мкм до 1 нм потребует более 40 лет. Разница в том, что если ранее цифровой символ в названии технологии отражал реальные минимальные проектные нормы элементов микросхемы (чаще всего размер затвора), то в настоящее время это только абстрактный маркетинговый символ, свидетельствующий о новом шаге в развитии технологии, но никак не реальные размеры элементов, создаваемые литографическими методами. Однако несмотря ни на что, у автора, вся жизнь которого связана с микроэлектроникой, эта эволюция вызывает восхищение. Еще 10 лет назад микроэлектронике предрекали закат и истощение из-за достижения физических ограничений при переходе даже к 10 нм. Теперь понятно, что рубеж в условный 1 нм для кремния может быть достигнут, а альтернативой горизонтальной интеграции для повы-

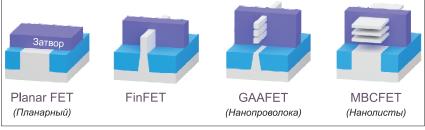

Рис. 1. Структура транзисторов Planar FET, FinFET, GAAFET, MBCFET

шения количества элементов микросхемы в корпусе давно стала вертикальная интеграция вначале в самом кристалле, а затем и в корпусе в виде 3D-сборки. Проблемы с размерами, которые ожидают нас впереди, будут решены так же, как и все предыдущие.

# ЭПОХА FINFET ТРАНЗИСТОРОВ ЗАКАНЧИВАЕТСЯ

Планарные МОП-структуры с затвором из диоксида кремния (Planar FET) с успехом применялись при создании транзисторных структур с проектными нормами выше 45 нм. При этом толщина затворного диэлектрика постоянно уменьшалась с целью увеличения емкости затвора, повышения производительности и быстродействия транзисторов. Диоксид кремния был очень удобным технологичным материалом, полностью совместимым с кремнием. Но уже при достижении толщины двуокиси кремния

менее 2 нм из-за повышения дефектности и эффекта туннелирования резко возрастали токи утечки и энергопотребление, что приводило к снижению надежности транзисторных структур и всего устройства.

В 2007 г. Intel заявила о замене диоксида кремния диэлектриком с высокой диэлектрической проницаемостью (high-k) на основе гафния в сочетании с металлическим затвором для транзисторов по 45-нм технологиям и внедрила их в серии процессоров 2007 г. под кодовым названием Penryn [1]. Об этом же сообщили и некоторые другие компании, в т. ч. IBM и NEC. Планарные МОП-структуры с высоким значением k и металлическим затвором использовались также в следующем поколении 32-нм технологии. Однако при достижении размера менее 25 нм дальнейшее масштабирование планарной транзисторной МОП-структуры стало невозможным. Ее заменила FinFET-структура трехмерного транзистора (см. рис. 1), изобретенного профессором Ху Чжэнмином из Калифорнийского университета в Беркли [2]. Intel запустила первый коммерческий 22-нм FinFET в 2011 г., а затем стала использовать их в 16/14 нм техпроцессах [3]. Именно FinFET-структура применялась во всех генерациях технологии, начиная с 22-нм до текущей

Таблица 1. История освоения технологий микроэлектроники

| Год        | 1971   | 1974   | 1977   | 1981    | 1984    | 1987   | 1990   | 1993   |  |

|------------|--------|--------|--------|---------|---------|--------|--------|--------|--|

| Технология | 10 мкм | 6 мкм  | 3 мкм  | 1,5 мкм | 1,0 мкм | 800 нм | 600 нм | 350 нм |  |

| Год        | 1996   | 1999   | 2001   | 2003    | 2005    | 2007   | 2009   | 2012   |  |

| Технология | 250 нм | 180 нм | 130 нм | 90 нм   | 65 нм   | 45 нм  | 32 нм  | 22 нм  |  |

| Год        | 2014   | 2016   | 2018   | 2020    | 2022*   | 2023*  | 2031** | 2034** |  |

| Технология | 14 нм  | 10 нм  | 7 нм   | 5 нм    | 3 нм    | 2 нм   | 1 нм   | 0,7 нм |  |

<sup>\*</sup> Прогноз. \*\* Прогноз IDRS.

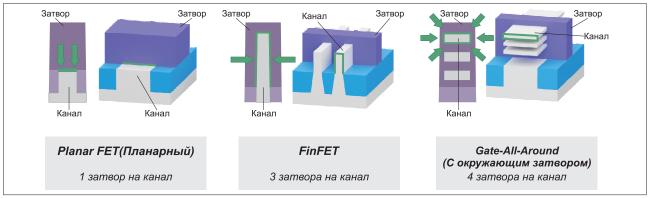

Рис. 2. В транзисторах GAAFET затвор имеет круговую структуру

5-нм. Однако размер в 3 нм равнозначен длине цепочки из нескольких десятков соединенных встык атомов кремния, т. к. радиус его атома равен 0.111 нм [4]. Понятно, что величина 3 нм является предельной для текущей конструкции FinFET-структуры транзистора, ограничивающей его дальнейшее использование. Практически все передовые компании рассматривают в настоящее время переход на структуры с круговым затвором GAAFET (Gate All-Around Field Effect Transistor) вместо FinFET для технологий 3 нм и менее. GAAFET использует ту же концепцию, что и FinFET, с той разницей, что затвор окружает канал с четырех сторон, а не с трех, как у FinFET, а вместо плавника (fin), от которого и произошло название этой технологии, применяются разные конструкции GAA (см. рис. 2). В настоящее время используются четыре основные технологии: нанопроволоки, многонаправленные перемычки в виде листовой структуры, нанопроволоки с гексагональным поперечным сечением и нанокольца. Более всего популярны структуры с нанолистами. Однако подходы разных компаний имеют отличия, которые могут серьезно отразиться на результатах и сроках при освоении технологий 3 нм и менее.

**TSMC.** Тайваньский мировой полупроводниковый технологический лидер уже много лет задает тон в разработке передовых технологий микроэлектроники. TSMC первой освоила самые

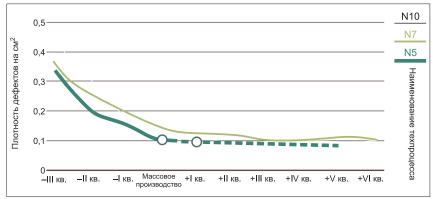

современные 7- и 5-нм технологии, благодаря чему уже в ноябре 2020 г. получила заказы по этим техпроцессам на все первое полугодие 2021 г. [5]. На ежегодном технологическом симпозиуме TSMC тайваньский производитель полупроводников подробно описал характеристики своего будущего 3-нм технологического узла, а также изложил дорожную карту для 5-нм технологических процессов N5P и N4 [6]. Техпроцесс N5, который представляет собой технологию 2-го поколения в глубоком ультрафиолете (DUV) и экстремальном ультрафиолете (EUV), находится в массовом производстве уже несколько месяцев. TSMC сообщила, что N5 прогрессирует с плотностью дефектов на четверть меньше, чем было в начале создания N7; при этом у N5 – лучше производительность при массовом производстве, чем у обоих предшественников N7 и N10. Предполагается, что плотность дефектов продолжит улучшаться. TSMC готовит новый техпроцесс N5P, основанный на текущей технологии N5, который увеличивает производительность и энергоэффективность за счет большей скорости на 5% и снижения мощности на 10%. Помимо N5P, TSMC также представила технологию N4, которая представляет собой дальнейшее развитие процесса N5 за счет дополнительных уровней EUV для уменьшения количества масок. Начало рискового производства N4 запланировано на IV кв. 2021 г., а массовое производство - на 2022 г.

Наибольший интерес представляет информация по 3-нм техпроцессу. В отличие от Samsung, выбравшей новую структуру GAAFET для 3-нм технологии, тайваньская компания решила использовать FinFET и добиться результата с помощью инновационного масштабирования. В таблице 2 сравниваются параметры микросхем для новых поколений 7-5-3-нм технологий TSMC [7]. По сравнению с N5, техпроцесс N3 обещает улучшить производительность на 10-15% при тех же уровнях мощности или снизить мощность на 25-30% при тех же скоростях транзистора. Кроме того, TSMC обещает увеличить плотность логической области в 1,7 раза, т. е. коэффициент масштабирования между логикой N5 и N3 станет равным 0,58. Это агрессивное снижение не распространяется напрямую на все структуры, поскольку плотность памяти SRAM улучшится только на 20%, что означало бы коэффициент масштабирования 0,8×, а аналоговые структуры масштабируются еще хуже при плотности 1,1×. Современные конструкции микросхем очень тяжелы для SRAM с практическим отношением 70/30 SRAM к логике, поэтому на уровне микросхемы кристалл, как ожидается, сократится только ~26% или того меньше. Планируется, что N3 выйдет на рисковое производство в 2021 г. и начнет массовое производство во II кв. 2022 г. Заявленные TSMC характеристики процесса на N3 будут точно соответствовать параметрам

Таблица 2. Заявленные улучшения параметров микросхем для новых поколений 7–5–3-нм технологий ТSMC

|                       | TSMC                          |                             |                             |                             |                            |                             |                            |  |  |  |

|-----------------------|-------------------------------|-----------------------------|-----------------------------|-----------------------------|----------------------------|-----------------------------|----------------------------|--|--|--|

|                       | N7<br>по сравнению<br>с 16FF+ | N7<br>по сравнению<br>с N10 | N7P<br>по сравнению<br>с N7 | N7+<br>по сравнению<br>с N7 | N5<br>по сравнению<br>с N7 | N5P<br>по сравнению<br>с N5 | N3<br>по сравнению<br>с N5 |  |  |  |

| Мощность, %           | -60                           | <-40                        | -10                         | -15                         | -30                        | -10                         | -2530%                     |  |  |  |

| Производительность, % | 30                            | ?                           | 7                           | 10                          | 15                         | 5                           | 10-15%                     |  |  |  |

| Область логики        |                               |                             |                             |                             | 0,55×                      |                             | 0,58×                      |  |  |  |

| Уменьшение, %         | 70                            | >37                         | _                           | ~17                         | -45                        | _                           | -42                        |  |  |  |

| (Плотность)           |                               |                             |                             |                             | (1,8×)                     |                             | (1,7×)                     |  |  |  |

| Массовое производство |                               |                             |                             | II кв. 2019 г.              | II кв. 2020 г.             | 2021 г.                     | 2 половина 2022 г.         |  |  |  |

Samsung для 3-нм GAAFET-процесса с точки зрения мощности и производительности, но будут более значительными с точки зрения плотности. Агрессивные планы Samsung по 3-нм технологии вынудили TSMC начать рисковое производство по этому техпроцессу в 2020 г.

Однако уже при переходе к 2-нм технологии TSMC отказывается от FinFET и использует структуру с круговым затвором GAA [8]. TSMC ранее сообщала, что ее исследования и разработки 2-нм техпроцесса будут осуществляться в Баошане и Синьчжу. Она также планирует построить четыре очень больших завода по производству пластин Р1-Р4 на площади более 90 га. Оценивая текущий прогресс TSMC в исследованиях и разработках 2-нм процесса, можно сделать вывод, что компания приступит в 2023 г. к пробному рисковому производству, а в 2024 г. – к массовому выпуску.

Samsung. Южнокорейский концерн Samsung, основной конкурент TSMC в новых технологиях, решил использовать другую тактику, чтобы не только догнать тайваньского конкурента, но и вырваться вперед. В освоении 7и 5-нм технологий он отставал от TSMC на 6-12 месяцев. Спрос на производство микросхем для мобильных коммуникаций по этим технологиям столь высокий, что TSMC не хватает производственных мощностей и Apple через пять лет была вынуждена снова обратиться к своему конкуренту в сегменте мобильных устройств Samsung с заказами на изготовление микросхем М1 [9].

За все время технологического соперничества с TSMC у Samsung впервые появилась возможность не только догнать, но и опередить тайваньскую компанию. И, похоже, что южнокорейский концерн решил воспользоваться этой возможностью, инвестируя гигантские суммы в разработку и освоение 3-нм технологии GAA. Согласно новому инвестиционному плану Samsung, на эти цели компания выделяет 116 млрд долл., в т. ч. 26 млрд долл. до конца

2020 г., в то время как TSMC - только 17 млрд долл. [10]. В начале 2020 г. Samsung заявила, что уже получила прототип транзистора по новой 3-нм технологии с круговым затвором [11]. Выпуск продукции по 3-нм техпроцессу Samsung запланировала на 2022 г., как и TSMC. Но, в отличие от тайваньской компании, которая будет использовать FinFET в самом последнем техпроцессе, Samsung первой в мире освоит технологию GAA, которая будет затем применяться в 2-нм процессе и, возможно, также в 1-нм. В этом отношении южнокорейский концерн получит несомненное преимущество во времени при условии положительного результата, а при неудаче – потеряет потенциальный рынок 3-нм заказов.

Крупнейшая компания Южной Кореи начнет массовое производство 3-нм чипов в 2022 г., как сообщил в октябре посетителям мероприятии только по приглашению один из руководителей подразделения производства чипов [12]. Эта цель, которая прежде не была заявлена, означает, что компания находится на пути к выпуску самых передовых полупроводников в отрасли в том же году, когда ее тайваньский соперник рассчитывает пройти этот рубеж. Как сообщил делегатам конференции исполнительный вице-президент по разработке платформы для фаундри-производства Пак Джэ Хонг, Samsung уже разрабатывает инструменты исходного проектирования с ключевыми партнерами. Если Samsung добьется успеха, это станет прорывом в реализации ее амбиций стать предпочтительным производителем микросхем для таких компаний как Apple и Advanced Micro Devices, которые в настоящее время ориентируются на работу с TSMC.

Теперь Samsung возглавляет наследник-миллиардер Джей Й. Ли, который хочет дать новый толчок развитию компании, чтобы она установила технологическое лидерство в таких передовых секторах как производство микросхем и сетей 5G для

обеспечения следующего этапа роста. Компания Samsung, уже являющаяся крупнейшим производителем компьютерной памяти и дисплеев, намеревается увеличить свою долю в мировом контрактном производстве чипов и логических микросхем с оборотом в 250 млрд долл., который будет стремительно расти с появлением искусственного интеллекта и беспроводных технологий 5-го поколения. Согласно данным TrendForce, в 2019 г. TSMC контролировала более половины рынка контрактного производства микросхем, тогда как у Samsung было всего 18%. Ли очень заинтересовался этим вопросом. В октябре он лично посетил штаб-квартиру ASML Holding NV в Нидерландах, чтобы обсудить поставку установок для EUV-литографии. Другие топ-менеджеры посетили крупные города мира от Сан-Хосе до Мюнхена и Шанхая, устраивая форумы новых технологий и обсуждая сделки. Видно, что Samsung делает решающую ставку на освоение новой технологии и захват рынка. В январе текущего года Samsung неожиданно заявила о планах строительства в США фабрики по 3-нм технологии и намерении инвестировать в этот проект более 10 млрд долл. Начало строительства запланировано на 2021 г., поставка и запуск оборудования, в т. ч. EUV-литографии на 2022 г., а начало производства на 2023 г. Несомненно, это решение вызвано планами TSMC по строительству завода в США, и южнокорейский гигант пытается опередить своего конкурента. Но главное, что эта гонка инвестиций мировых лидеров TSMC и Samsung на американской территории только на пользу США, что можно считать победой политики американской администрации.

IMEC. Ведущий европейский исследовательский центр IMEC, расположенный в Бельгии, считает структуру с GAA круговым затвором MBCFET (Multi Bridge Channel FET) прогрессивной, но не идеальной для применения [13]. Идеальной, с точки зрения бель-

Рис. 3. Транзистор Forksheet с раздельными нанолистами, предложенный IMEC

гийцев, для техпроцессов менее 3 нм является другая транзисторная архитектура, которую они предлагают. В ІМЕС разработали транзистор с раздельными листами, или Forksheet. Это те же вертикальные нанолисты в качестве каналов транзисторов, но разделенные вертикальным диэлектриком (см. рис. 3). С одной стороны диэлектрика создается транзистор с *n*-каналом, с другой – с *p*-каналом. И оба они окружены общим затвором в виде вертикального ребра. Этот диэлектрик физически изолирует траншею с р-образным затвором от траншеи с *п*-образным затвором, обеспечивая гораздо более плотное расстояние между n- и p-областями. Данную проблему нельзя было решить с помошью FinFET или структур нанолистов. Из-за этого меньшего разделения пи р-областей ожидается, что нанолисты обеспечат превосходную масштабируемость по площади и производительности. Сократить расстояние на кристалле между транзисторами с разной проводимостью - еще одна главная задача для дальнейшего масштабирования изделия и техпроцесса. Моделирование TCAD подтвердило, что транзистор с раздельными страницами уменьшит площадь кристалла на 20%. В общем случае новая архитектура транзистора снизит стандартную высоту логической ячейки до 4,3 треков. Ячейка станет проще, что также относится к изготовлению ячейки памяти SRAM. Простой переход от нанолистового транзистора к транзистору с раздельными

нанолистами обеспечит прирост производительности на 10% с сохранением потребления или сокращение потребления на 24% без прироста производительности.

Молелирование 2-нм техпроцесса показало, что ячейка SRAM с использованием раздельных нанолистов обеспечит комбинированное уменьшение площади и повышение производительности до 30% при разнесении *p*- и *n*-переходов до 8 нм. По мере того как отрасль масштабируется от плоского до FinFET и вертикально уложенных нанолистов, концепция Forksheet считается улучшающим расширением, считает Жюльен Рикаерт, директор программы трехмерного гибридного масштабирования в ІМЕС. Устройство с нанолистом в основном было введено для улучшения контроля над электростатическим разрядом и повышения прочности. Однако не только для FinFET, но и для архитектуры нанолистов характерно большое расстояние между областями n- и p-типа, что препятствует дальнейшей масштабируемости. Архитектура Forksheet – один из способов решения этой проблемы, и ее можно рассматривать как «универсальное» КМОПустройство с максимальной логикой за пределами 2 нм. Масштабирование за пределы Forksheet предлагает дополнительный полевой транзистор (или CFET) в качестве такого устройства, утверждает Жюльен Рикаерт. Технологический процесс для Forksheet аналогичен процессу для устройства

с нанолистом, только с ограниченными дополнительными этапами процесса. Еще в 2018 г. ІМЕС предложил новый материал металлизации для микросхем по технологии менее 5 нм. Традиционный металл – медь – становится проблемным для этих процессов из-за сложности масштабирования, возрастающих проблем по показателю сопротивление/емкость и надежности. ІМЕС предложил рутений (Ru) в качестве нового материала межсоелинений [14]. По утверждению ІМЕС, межкомпонентные соединения на основе Ru являются многообещающими кандидатами из-за их устойчивости к окислению, высокой температуры плавления, низкого объемного удельного сопротивления и способности создавать безбарьерные межкомпонентные модули.

Intel. Информации о состоянии с развитием технологии 3 нм и менее у американской компании очень мало. По тем сведениям, которые просачиваются, Intel тоже работает над этими техпроцессами, хотя еще не придумала названия своим транзисторам. Компания делает ставку на кольцевую архитектуру GAA, но пока не понятно, в каком варианте исполнения: с нанопроволокой или с нанолистами. Несколько лет назад Intel называла срок внедрения этой технологии – 2023 г. Однако учитывая технологический кризис процессорного гиганта, неспособного освоить даже техпроцесс 7 нм, и отсутствие конкретной информации о ходе работ, этот срок вызывает сомнения. В конце

Рис. 4. **Стратегия Intel по новым технологиям в диапазоне 10–1,4 нм**

Таблица 3. Дорожная карта развития технологий от 7 нм до 0,7 нм, разработанная IRDS

|                                                                   | G54M36                  | G48M30                              | G45M24                                                                         | G42M21                                                                     | G40M16                                         | G40M16T2                                                          |

|-------------------------------------------------------------------|-------------------------|-------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------|

| Обозначение проектных норм в индустрии логических приборов, нм    | 7                       | 5                                   | 3                                                                              | 2.1                                                                        | 1.5                                            | 1.0 eq                                                            |

| Обозначение проектных<br>норм IDM-Foundry                         | i10-f7                  | i7–f5                               | i5–f3                                                                          | i3–f2.1                                                                    | i2.1–f1.5                                      | i1.5e-f1.0e                                                       |

| Варианты<br>транзисторной<br>структуры для<br>логических приборов | FinFET                  | FinFET                              | FinFET; LGAA                                                                   | LGAA                                                                       | LGAA                                           | LGAA-3D                                                           |

| Основной тип структуры<br>для логических<br>приборов              | FinFET                  | FinFET                              | FinFET                                                                         | LGAA                                                                       | LGAA                                           | LGAA-3D                                                           |

| Технология литографии<br>для межсоединений                        | 193i, EUV               | 193i, EUV DP                        | 193i, EUV DP                                                                   | 193i, High-NA EUV                                                          | 193i, High-NA EUV                              | 193i, High-NA EUV                                                 |

| За пределами КМОП<br>для улучшения КМОП                           | _                       | -                                   | -                                                                              | Прибор 2D, FeFET*                                                          | Прибор 2D, FeFET                               | Прибор 2D, FeFET                                                  |

| Материал канала<br>транзистора                                    | Si                      | SiGe25%                             | SiGe 50%                                                                       | Ge, 2D-материалы                                                           | Ge, 2D-материалы                               | Ge, 2D-материалы<br>материалы                                     |

| Переход на новые<br>технологии                                    | Конформное<br>осаждение | Конформное<br>легирование, контакты | Контакты                                                                       | Стековые приборы, замена<br>Си металлизации Мх**                           | Стековые приборы, замена<br>Си металлизации Мх | 3D СБИС                                                           |

| Поколение структуры<br>стековой интеграции                        | 2D                      | 2D                                  | 3D-структура:<br>уменьшение размера<br>транзистора и чипа,<br>память на логике | 3D-структура: уменьшение размера транзистора и чипа, память на логике VGAA |                                                | 3D-структура,<br>3D СБИС: память<br>на логике,<br>применение VGAA |

<sup>\*</sup> FeFET — транзистор для ячеек памяти с использованием сегнетоэлектриков

\*\* Мх — металлизация с малым шагом.

2019 г. глава Intel представил стратегию освоения новых технологий, предусматривающую на ближайшие 10 лет более высокие темпы смены техпроцессов. Она предусматривает их смену через каждые два года с промежуточными усовершенствованиями при неизменных размерах через каждый год (см. рис. 4) [15]. Через год после освоения нового процесса должна появиться улучшенная версия с одним условным плюсом, а еще через год – с двумя плюсами. Через два года должен запуститься новый процесс с меньшими проектными нормами, который будет перекрываться с усовершенствованным процессом предыдущего поколения. К 2029 г. должен быть освоен 1,4-нм техпроцесс с использованием фотолитографии с высоким значением цифровой апертуры NA (High-NA EUV). Это смелый план, который 10 лет назад был бы воспринят с энтузиазмом и доверием. Но провал Intel с освоением 10- и 7-нм процессов наводит на мысль, что сильное отставание процессорного гиганта от конкурентов не оставляет ему другого выхода кроме значительно ускоренного освоения новых технологий в ближайшие годы, а главное, продукции, изготовленной с их помощью. Не стоит забывать, что Intel многие десятилетия была не только мировым лидером продаж, но и технологическим авангардом и инициатором многих мировых новшеств. Так что у нее есть возможность сделать опережающий рывок и вернуть себе все регалии. Решение о замене главы Intel, финансиста по образованию, техническим профессионалом, ранее работавшим в компании, свидетельствует о серьезности намерений прервать затянувшийся кризис. К тому же, Intel серьезно рассматривает возможность аутсорсинга в TSMC и Samsung по изготовлению своих 5-нм кристаллов.

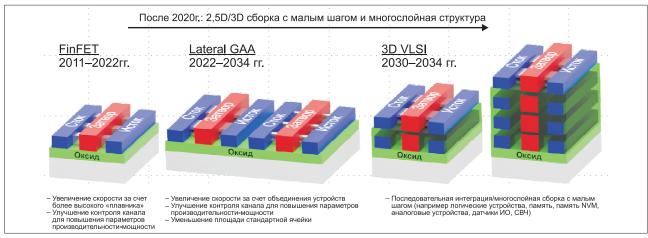

IRDS. «Больше Мура». Международная группа экспертов под эгидой IEEE (Institute of Electrical and Electronics Engineers – Институт инженеров электротехники и электроники) разрабатывает стратегию развития мировой полупроводниковой промышленности IRDS (International Roadmap for Devices and Systems). В 2020 г. они опубликовали дорожную карту «Больше Мура» по развитию полупроводниковых технологий до 1 нм и менее (см. табл. 3) [16]. IRDS ожидает, что полевые транзисторы GAA (Gate-all-around) и FinFET будут одновременно использоваться в 3-нм технологии, а GAAFET заменят FinFET уже в 2-нм техпроцессе. Аббревиатура LGAAFETS относится к полевым транзисторам с боковым затвором или полевым транзисторам GAAFET в традиционном 2D-формате. Полевые транзисторы с вертикальным затвором VGAA будут использоваться в трехмерных транзисторных структурах, которые еще не разработаны. IRDS также прогнозирует использование 193-нм литографии до 2034 г., не давая никаких объяснений по этому поводу в отчете. Эксперты IRDS прогнозируют развертывание после 2025 г. EUV-технологии с высоким значением числовой апертуры NA (безразмерное число, характеризующее диапазон углов, в которых система принимает или излучает свет). Альтернативой EUV с высоким NA является немедленный переход к EUV с множественным экспонированием. По прогнозу IRDS, внедрение 1-нм технологии ожидается в 2031 г.

В первые годы до 130-нм процесса транзисторы пользовались масштабированием Деннарда, где эквивалентная толщина оксида (ЕОТ), длина затвора транзистора (Lg) и ширина транзистора (W) масштабировались с постоянным коэффициентом, чтобы улучшить задержку при постоянной плотности мощности. В настоящее время существует множество входных параметров, которые можно изменять, а выходные параметры являются сложными функциями этих входных параметров. Таким образом, для достижения той же цели

Рис. 5. Дорожная карта архитектуры приборов больше Мура по прогнозу IRDS

могут быть найдены разные сценарии масштабирования. Чтобы поддерживать масштабирование при низких напряжениях, в последние годы использовались, главным образом, дополнительные решения для повышения производительности – напряжение в канале, стимуляторы стресса, металлический затвор с высоким k, снижение контактного сопротивления и улучшение электростатики. При этом компенсировались потери управления затвором, тогда как для высокопроизводительных мобильных приложений необходимо уменьшить напряжение питания. FinFET по-прежнему остается ключевой архитектурой устройства, которая может поддержать масштабирование до 2025 г. Электростатика и уменьше-

ние количества ребер (т. е. увеличение высоты ребер при уменьшении количества ребер на единицу площади основания) остаются двумя эффективными решениями для повышения производительности. Ожидается, что улучшение паразитных свойств останется основным фактором повышения производительности в результате ужесточения правил проектирования. Прогнозируется, что паразиты останутся доминирующим термином в работе критических узлов. Для пониженного напряжения питания потребуется переход к структурам GAA, таким как боковые нанолисты, чтобы поддерживать управление затвора за счет лучшей электростатики. Боковая структура GAA в конечном итоге будет развиваться в гибридной

форме с вертикальной структурой GAA, чтобы вернуть потерю производительности из-за увеличения паразитных характеристик на более узких частотах, а также для специализированных функций системы-на-кристалле (СнК), к которым относится селектор памяти. Последовательная интеграция позволит размещать устройства друг на друге с помощью монолитной 3D-интеграции. Фокус масштабирования сместится с увеличения производительности однопотокового режима на снижение энергопотребления, а затем перейдет к высокопараллельным трехмерным архитектурам, обеспечивающим работу с низким напряжением питания и большим количеством функций, встроенных в единицу объема.

Таблица 4. Дорожная карта IRDS параметров СнК для разных технологий

|                                                                                 | G48M36 | G45M24       | G42M20  | G40M16    | G38M16T2    | G38M16T4    |

|---------------------------------------------------------------------------------|--------|--------------|---------|-----------|-------------|-------------|

| Обозначение проектных норм в индустрии логических приборов, нм                  | 5      | 3            | 2.1     | 1,5       | 1,0 eq      | 0,7 eq      |

| Обозначение проектных норм IDM-Foundry                                          | i7–f5  | i5-f3        | i3-f2.1 | i2.1-f1.5 | i1.5e-f1.0e | i1.0e-f0.7e |

| Варианты структуры логических приборов                                          | FinFET | FinFET, LGAA | LGAA    | LGAA      | LGAA-3D     | LGAA-3D     |

| Основной тип структуры логических приборов                                      | FinFET | FinFET       | LGAA    | LGAA      | LGAA-3D     | LGAA-3D     |

|                                                                                 | Ocean  | Ocean        | Ocean   | Ocean     | Occup       | Occus       |

| Напряжение питания Vdd, B                                                       | 0,70   | 0,70         | 0,65    | 0,65      | 0,60        | 0,60        |

| Длина затвора, мм                                                               | 18     | 16           | 14      | 12        | 12          | 12          |

| Количество уровней                                                              | 1      | 1            | 1       | 1         | 2           | 4           |

| Количество уровней устройств                                                    | 1      | 1            | 3       | 3         | 4           | 4           |

| Масштабирование цифровой области — техпроцесс к техпроцессу                     |        | 0,75         | 0,78    | 0,79      | 0,52        | 0,50        |

| Ограничение высоты ячейки — HD                                                  | MO     | MO           | MO      | MO        | МО          | МО          |

| Масштабирование области СнК (многослойная структура) — техпроцесс к техпроцессу |        | 0,78         | 0,82    | 0,83      | 0,56        | 0,59        |

| Частота цифрового процессора (ЦП), ГГц                                          | 3,13   | 3,27         | 3,51    | 3,47      | 3,25        | 2,93        |

| Частотное масштабирование — техпроцесс к техпроцессу                            |        | 0,04         | 0,08    | -0,01     | -0,07       | -0,10       |

| Частота ЦП при постоянной удельной мощности, ГГц                                | 3,13   | 2,58         | 2,92    | 2,19      | 1,29        | 0,78        |

| Мощность при равных частотах — техпроцесс к техпроцессу                         |        | -0,08        | -0,26   | -0,05     | -0,07       | -0,09       |

Хотя архитектуры устройств претерпевают изменения, ожидается, что последующие модули также будут развиваться. Они могут включать: 1) исходные подложки, например Si для структур кремния на изоляторе (SOI); 2) материал канала эволюционирует от Si до SiGe, Ge, материалов группы III–V; 3) контактный модуль, эволюционирующий от силицидов к новым материалам, обеспечивающим меньшую высоту барьера Шоттки (SBH), и к схемам интеграции с объемным контактом для увеличения площади контактной поверхности.

После 2022 г. ожидается начало перехода на архитектуру с латеральным устройством GAA, но для трехмерных гибридных приложений с памятью на логике потенциально могут применяться гибридные вертикальные устройства GAA с латеральными GAA. С 2031 г. ожидается внедрение вертикальных 3D-структур памяти на логике, логики на логике. Эволюция и развитие архитектур устройств с использованием 3D показано на рисунке 5.

Прогнозируемое изменение мощности и производительности системына-кристалле приведено в таблице 4. В технологиях 5 и 1 нм напряжение питания микросхем изменится слабо с 0,7 до 0,6 В, а плотность мощности вырастет в 3,7 раза, в первую очередь благодаря 3D-структурам. Предполагается, что тактовая частота незначительно повысится до 3,5 ГГц в 2025 г. в результате изменения паразитных параметров и ограничения управления затвором ( $V_{GS} - V_{T}$ ) в зависимости от масштабирования. После 2028 г. тактовая частота цифровых процессоров ухудшится из-за увеличения паразитных характеристик в стандартной ячейке и соединениях, хотя 3D СБИС помогает масштабировать длину проводов из-за уменьшения площади цифрового блока за счет разделения ячеек в 3D-структуре. Кроме того, тепловые ограничения (увеличение плотности мощности) снижают среднюю частоту до 0,8 ГГц. По сути, если ничего не делается для уменьшения тепловых проблем. необходимо чаще модифицировать процессор, чтобы поддерживать ту же плотность мощности. Скорость снижения мощности имеет тенденцию к сглаживанию из-за уменьшения напряжения питания (Vdd) и замедления изменения емкости к итоговому сроку дорожной карты.

## ПРОТИВОРЕЧИЯ И КОНФЛИКТЫ 5-И 3-нм ТЕХНОЛОГИЙ

Полевые транзисторы на основе нанолистов появились в 2017 г., когда Samsung представила многоблочный

полевой транзистор (MBCFET) на 3-нм техпроцессах. МВСГЕТ - полевой транзистор с нанолистом. TSMC также работает над нанолистами. В течение многих лет в исследованиях и разработках использовался полевой транзистор с нанолистом – один из типов транзисторов с круговым затвором. Нанолист обеспечивает умеренное повышение мощности и быстродействия по сравнению с 5-нм полевыми транзисторами, но у нанолистов имеются некоторые преимущества. Транзистор с нанолистом – это, по сути, полевой транзистор на своей стороне с обернутым вокруг него затвором. Нанолист состоит из нескольких тонких горизонтальных частей или листов. уложенных вертикально друг на друга. Каждый лист составляет канал и окружен затвором, создавая транзистор, который работает по всему периметру.

Теоретически полевые транзисторы с нанолистами обеспечивают более высокую производительность при минимальной утечке, поскольку контроль тока осуществляется с помощью четырех сторон структуры. Сначала нанолисты будут состоять из четырех или около того листов. По словам Хоригучи из ІМЕС [17], типичная ширина нанолиста составляет 12-16 нм, а толщина – 5 нм. Этим нанолисты отличаются от FinFET, имеющих ограниченное количество ребер, что создает некоторые ограничения при разработке. «Преимущество нанолиста в том, что он может иметь разную ширину у каждого устройства, что дает некоторую свободу разработчикам, позволяя найти лучшее решение для повышения производительности и мощности», - считает Хоригучи. Например, у транзистора с более широким листом управляющий ток будет больше. Узкий лист позволяет использовать меньшее устройство с меньшим током управления. Нанолист взаимосвязан с нанопроволокой и вместо них в качестве каналов можно использовать нанопроволоку. Ширина канала снижается, что уменьшает управляющий ток. Благодаря этому обстоятельству полевые транзисторы на основе нанолистов набирают обороты. Однако имеется несколько проблем для этой технологии и FinFET на 3 нм или около этого. «Проблемы FinFET связаны с контролем ширины и профиля ребра при большей длине затвора. Проблемы с нанолистами – дисбаланс n- и p-областей, эффективность нижнего листа, промежуточная прокладка, контроль длины затвора и покрытие рельефа структуры», – считает Цзинь Цай, заместитель директора TSMC. на презентации на конференции IEDM.

Требуется время, чтобы освоить и начать совершенствовать полевые транзисторы на основе нанолистов. «Существует много проблем, связанных с переходом на новую транзисторную архитектуру, - заявил Герреро из Brewer Science. – Безусловно, потребуются новые материалы». В простом технологическом процессе полевой транзистор с нанолистом начинается с формирования сверхрешеточной структуры на подложке. Эпитаксиальным нарашиванием наносят на подложку чередующиеся слои кремний-германий (SiGe) и кремний. Как минимум, стопка должна состоять из трех слоев SiGe и трех слоев кремния. Затем вертикальные ребра формируются в структуре сверхрешетки с использованием рисунка и травления. Для структуры сверхрешетки и формирования требуется точное управление и прецизионный контроль. Затем следует один из самых сложных шагов - создание внутренних распорок. Во-первых, внешние части слоев SiGe в сверхрешеточной структуре утоплены. Это создает небольшие пространства, заполненные диэлектрическими материалами. «Внутренние прокладки необходимы для уменьшения емкости между затвором и истоком - стоком», - сообщил Цай из TSMC. - Контроль процесса создания внутренней прокладки очень важен». IBM и TEL недавно описали новую технику травления не только для внутреннего спейсера, но и для процесса формирования канала. Он включает анизотропную технику сухого травления SiGe с соотношением (анизотропией) 150:1. Эта технология позволяет использовать точные внутренние распорки. «Для встраивания SiGe требуется высокоселективное боковое «слепое» травление жертвенных слоев SiGe, - отмечается в статье Николя Лубе, менеджера по исследованиям и разработкам ІВМ. Затем формируются исток-сток. После этого слои SiGe в сверхрешеточной структуре удаляются с помощью травления. Остаются слои или листы на основе кремния, из которых состоят каналы. Далее осаждается диэлектрик с высокой диэлектрической проницаемостью (high-k), формируются контакты MOL (Middle-Of-The-Line), межсоединения из меди, в результате чего образуется нанолист. Тем не менее, как и в случае с любой новой технологией, нанолисты могут подвергаться дефектам. Это требует большего количества этапов проверки и метрологии в производстве.

«Как и при предыдущих изменениях архитектуры, мы сталкивались с проблемами контроля и метрологии, связанны-

ми с нанолистами», – заявил Чет Ленокс, директор по управлению технологическими процессами контроля, компания КLA. Это также требует новых методов. Например, IMEC и Applied Materials недавно представили доклад о методе сканирующей микроскопии сопротивления растеканию (s-SSRM) для кругового контроля затвора. В s-SSRM крошечный скальпель рассекает небольшую часть структуры, обеспечивая контроль поперечного сечения для профилей легирующих примесей.

Проблемой при переходе к меньшим размерам становятся ограничения при формировании контактов MOL и межсоединений BEOL (Back-End-Of-The-Line). Как правило, шаг по затвору 7-нм процесса составляет 56-57 нм, шаг по металлу – 40 нм, а 5-нм процесс, соответственно, 45-50 и 26 нм. Как полагают некоторые специалисты, при переходе с технологии 5 нм на 3 нм процессы создания контактов MOL и межсоединений BEOL станут ограничивающим фактором, снижающим преимущества масштабирования до значений не выше 8%. Проблемой становятся рост удельного контактного сопротивления, увеличение сопротивления межсоединений и паразитных емкостей.

По мнению автора настоящей статьи, самой сложной производственной проблемой при освоении технологий 3 нм и менее может стать критическое влияние дефектности на качество и выход годных. Плотность и размеры дефектов становятся определяющими. Именно эту проблему долго не могла решить Intel при освоении техпроцесса 10 нм. Кроме того, если ранее в FinFETструктурах любой критический дефект приводил к браку одного транзистора, то в нанолистовых структурах выходит из строя целый стек транзисторов. Резко возрастает также цена человеческих ошибок, качества чистых помещений, чистоты технологических материалов, газов и энергоносителей. Именно эту проблему так и не смогла до конца решить советская микроэлектроника, хронически проигрывавшая зарубежной в выходе годных и пропорциональной себестоимости.

# ЭКОНОМИКА НОВЫХ ТЕХНОЛОГИЙ И СОВРЕМЕННЫХ КРИСТАЛЛОВ

Разработка и освоение новых 7-нм и меньше технологий является крайне дорогостоящей, доступной только нескольким компаниям в мире. Потенциально их способны реализовать только TSMC, Samsung и пока еще Intel, хотя последняя все больше отстает от первых двух. Вероятнее всего именно TSMC и Samsung станут единственными в мире контрактными фаундри–производите-

Таблица 5. Количество EUV-степперов, требуемое для производства микросхем логики и памяти

| Рынок                  | Производственная мощность<br>фабрики, тыс. пл./мес. | Слои EUV | Кол-во EUV-степперов<br>на фабрику |  |  |

|------------------------|-----------------------------------------------------|----------|------------------------------------|--|--|

| Логика (7—5 нм)        | 45                                                  | 10-20    | 10-20                              |  |  |

| Память DRAM (16—10 нм) | 100                                                 | 1–6      | 2–10                               |  |  |

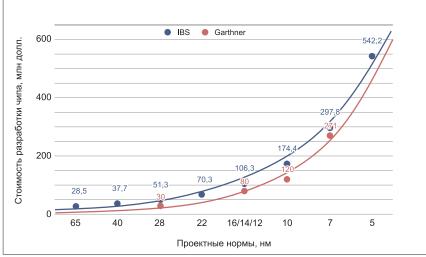

Рис. 6. Стоимость разработки чипов по технологиям 65-5 нм от компаний IBS и Gartner

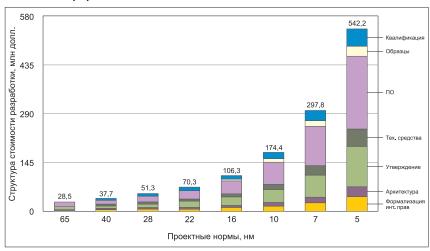

Рис. 7. **Структура стоимости разработки чипов по технологиям от 65 до 5 нм от IBS**

лями чипов по 5–3–2-нм технологиям. По расчетам компании IBS, разработка 3-нм процесса может стоить 4–5 млрд долл., а строительство завода производительностью 40 тыс. пластин в месяц обойдется в гигантские 15–20 млрд долл. [18]. Стоимость современного степпера не самой последней конфигурации для EUV-фотолитографии для 7 нм достигает

120 млн долл. [19], что соизмеримо с ценой новых лайнеров Airbus A320 или Boeing 737 Мах. Цена новых моделей с повышенной производительностью может доходить до 200 млн долл., а это уже цена Boeing 767. При производительности системы TWINSCAN NXE 3400B 125 пластин в час, а для TWINSCAN NXE 3400C – 175 пластин в час [20] современ-

Таблица 6. Расчет стоимости пластин и кристаллов по технологиям 16—5 нм на примере чипов Apple

|                                                     | 16 нм   | 10 нм   | 7 нм    | 5 нм     | 3 нм     |

|-----------------------------------------------------|---------|---------|---------|----------|----------|

| Площадь чипа, мм²                                   | 125,00  | 87,66   | 83,27   | 85,00    | 85,00    |

| Количество транзисторов, млрд                       | 3,3     | 4,3     | 6,9     | 10,5     | 14,1     |

| Общее кол-во чипов на пластине                      | 478     | 686     | 721     | 707      | 707      |

| Кол-во годных чипов на пластине                     | 359,74  | 512,44  | 545,65  | 530,25   | 509,04   |

| Стоимость пластины, долл.                           | 5912,00 | 8389,00 | 9965,00 | 12500,00 | 15500,00 |

| Стоимость чипа, долл.                               | 16,43   | 16,37   | 18,26   | 23,57    | 30,45    |

| Стоимость транзистора на 1 млрд транзисторов, долл. | 4,98    | 3,81    | 2,65    | 2,25     | 2,16     |

Таблица 7. Экономика и расчет производственных затрат и стоимости пластин, чипов для технологий 90–5 нм

| Nº | Проектные нормы, нм                                                                                                   | 90                | 65                | 40               | 28                | 20                 | 16/12              | 10                | 7                  | 5                |

|----|-----------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|-------------------|--------------------|--------------------|-------------------|--------------------|------------------|

| 1  | Квартал и год запуска массового производства                                                                          | IV кв.<br>2004 г. | IV кв.<br>2006 г. | I кв.<br>2009 г. | IV кв.<br>2011 г. | III кв.<br>2014 г. | III кв.<br>2015 г. | II кв.<br>2017 г. | III кв.<br>2018 г. | I кв.<br>2020 г. |

| 2  | Капитальные вложения из расчета на изготовленную пластину в год, долл.                                                |                   | 5456              | 6404             | 8144              | 10356              | 11220              | 13169             | 14267              | 16746            |

| 3  | Чистая амортизация капитала с начала 2020 г. (25,29% в год)                                                           | 65%               | 65%               | 65%              | 65%               | 65%                | 65%                | 55,1%             | 35,4%              | 0,0%             |

| 4  | Неамортизированный капитал из расчета на изготовленную пластину в год (остаточная стоимость на начало 2020 г.), долл. | 1627              | 1910              | 2241             | 2850              | 3625               | 3927               | 5907              | 9213               | 16746            |

| 5  | Затраты на износ из расчета на изготовленную пластину в 2020 г., долл.                                                | 411               | 483               | 567              | 721               | 917                | 993                | 1494              | 2330               | 4235             |

| 6  | Прочие расходы и суммы, приходящиеся на пластину, долл.                                                               | 1293              | 1454              | 1707             | 2171              | 2760               | 2990               | 4498              | 7016               | 12753            |

| 7  | Стоимость фаундри-производства из расчета на пластину, долл.                                                          | 1650              | 1937              | 2274             | 2891              | 3677               | 3984               | 5992              | 9346               | 16988            |

| 8  | Стоимость фаундри-производства из расчета на чип, долл.                                                               | 2433              | 1428              | 713              | 453               | 399                | 331                | 274               | 233                | 238              |

Рис. 8. Плотность дефектов в производстве TSMC для 10-7-5-нм процессов

ному производству мощностью 45 тыс. пластин в месяц требуется 10 и более установок (см. табл. 5) [21]. Это значит, что только стоимость EUV-установок на современной фабрике по технологии 5 нм превысит 1 млрд долл. Одновременно с этим постоянно растет и стоимость разработки чипов по современным технологиям. На рисунке 6 приведены цена затрат по разработке чипов по технологиям 65–5 нм по данным компаний IBS и Gartner [22].

На рисунке 7 показан рост затрат на проектирование и их структура для этих же проектных норм по расчетам компании IBS [23]. Видно, что затраты на дизайн поднялись с 51,3 млн долл. для разработки микросхем по 28-нм технологии до 297,8 млн долл. для чипа на 7 нм и 542,2 млн долл. для 5 нм, а самую большую долю в цене составляет разработка программного обеспечения. Однако уже для микросхем на уровне 3 нм диапазон затрат будет колебаться в пределах между 500 млн и 1,5 млрд долл. в случае самых сложных микросхем от Nvidia. По мере того как сложность полупроводников растет, возникает потребность в высококвалифицированных специалистах и увеличении средств проектирования и изготовления. Эффективное количество дизайнеров, определяемое путем деления расходов на НИОКР в области полупроводников на заработную плату высококвалифицированных работников, выросло в 18 раз с 1971 по 2015 гг. Другими словами, для удвоения количества транзисторов на кристалле в соответствии с законом Мура в 2015 г. потребовалось в 18 раз больше исследований и людей, чем в 1971 г., что равнозначно ежегодному увеличению на 7%. Общая стоимость проектирования и производства в пересчете на один транзистор может быть лучшим показателем, чтобы оценить, остается ли повышение плотности транзисторов экономичным. Эта стоимость исторически ежегодно снижалась примерно на 20-30%. Однако по этому поводу нет единого мнения. Некоторые аналитики утверждают, что снижение остановилось после введенного узла 28 нм в 2011 г., тогда как другие не согласны с этим выводом.

Усложнение технологий сопровождается значительным повышением стоимости пластины, снижением выхода годных чипов с пластины и повышением стоимости кристалла. Так, расчеты на примере процессоров А11-А14 для айфонов показывают, что стоимость пластины с 5-нм кристаллами достигнет 12500 долл., а в случае использования 3-нм техпроцесса – 15500 долл. (по другим расчетам, – 16 998 долл. [22]), тогда как количество годных чипов с пластины упадет с 530 до 509, соответственно (см. табл. 6–7) [23]. Таким образом, цена одной пластины по 3-нм технологии и ниже становится почти равной стоимости нового автомобиля

Тоуота Corolla. В то же время расчетная стоимость одного транзистора постоянно снижается. Компания TSMC за счет строительства более современных технологических помещений и внедрения фотолитографии EUV в экстремальном диапазоне в каждом процессе от 10 нм до 7 и 5 нм снижает дефектность процесса (см. рис. 8) [24], что способствует снижению себестоимости производства после начала освоения.

Очевидно, что и сфера контрактного производства, и сфера проектирования микросхем по технологиям менее 5 нм становятся уделом избранных и очень богатых компаний в мире. Они должны вложить гигантские средства в разработки, производство и обеспечить быструю оборачиваемость таких изделий на рынке. Реализовать такие условия могут только постоянно обновляемые изделия массового мирового потребительского рынка для населения и, в первую очередь, в сфере коммуникаций. Россия, как и СССР, никогда в своей истории не обладала способностями и конкурентоспособностью в осуществлении таких задач. Именно поэтому наша страна всегда будет зависеть в этой сфере от возможностей мирового рынка, а оборонный комплекс любой страны должен будет ориентироваться на выпуск и применение сложных изделий с гражданского рынка. В противном случае, особенно при наличии такого собственного производства, единичный выпуск этой сложной продукции способен разорить бюджет любого государства.

## KTO ВЫИГРАЕТ – SAMSUNG ИЛИ TSMC?

Шаг эволюции от FinFET-транзисторов к GAAFET, универсальный затвор в новой технологии обеспечивают лучшую производительность, но новые транзисторы трудны в изготовлении, дороги, и переход на них может оказаться болезненным. Положительным моментом является то, что производители оборудования уже занялись решением данных проблем, готовят новое

оборудование и технологии травления, метрологии, что поможет упростить этот переход. Тем не менее, шаг TSMC по расширению FinFET до 3 нм многим представляется более логичным. Переход на новый транзистор может создать потенциальные проблемы для клиентов. Они должны взвесить компромиссы по стоимости и техническим характеристикам новых изделий. Расширение FinFET - более безопасный путь. Многие заказчики считают риски TSMC меньшими в сравнении с Samsung. Однако южнокорейцы многое поставили на новую архитектуру и технологию и намерены выиграть. Время покажет, кто первый достигнет цели. Ждать осталось не долго.

### выводы

- Эпоха применения архитектуры FinFET транзисторов в современных сверхсложных интегральных микросхемах завершится на 3-нм технологии.

- 2. Начиная с 3-нм техпроцесса, компания Samsung переходит на транзисторы с круговым затвором GAAFET вместо FinFET, а TSMC планирует этот переход с 2-нм технологии. Между этими двумя компаниями развернется основная конкурентная борьба на поле технологий 3- и 2-нм.

- 3. Компания Samsung рассчитывает опередить TSMC быстрым освоением технологии GAAFET, получить преимущества в сроках и захвате мирового контрактного рынка при освоении 3- и 2-нм технологии. Тем самым Samsung намерена повторить и воспроизвести успех TSMC по 7- и 5-нм техпроцессам.

- 4. Компания Intel почти закрыла свое информационное пространство по разработке новых технологий, но заявляет об амбициозном труднореализуемом плане освоения 1,4-нм техпроцесса к 2029 г.

- 5. Конструкции транзисторных структур для субнанометровых (около 1 нм и менее) технологий еще не одобрены, но наиболее перспективными выглядят предложения IMEC по технологии CFET с раздельными нанолистами. Неотъемлемым элементом субнанометровых продуктов станут решения с вертикальной и горизонтальной 3D-интеграцией.

- 6. Эволюция и переход на субнанометровые структуры будут сопровождаться возрастанием роли паразитных эффектов, емкостей и параметров, увеличением роли процессов МОL и BEOL из-за увеличения удельного сопротивления контактов, которое потребует использования объемных контактов и металлизации межсоединений с меньшим удельным

- сопротивлением. Все это будет ограничивать эффекты масштабирования размеров элементов и чипов.

- Этот переход также потребует разработки не только нового оборудования для формирования наноструктур, и в первую очередь для травления, но и метрологического оборудования для контроля производственного процесса.

- 8. Резкий рост стоимости современных фабрик по 7-5-3-нм техпроцессам, достигающий 15-20 млрд долл., и стоимости проектирования сверхбольших интегральных микросхем по этим технологиям, составляющий 500-1500 млн долл., три-пять лет назад привел к значительной дифференциации контрактных производителей пластин, а в настоящее время и фаблесс-компаний, способных осуществлять и окупать такие расходы. Разработка и производство современных ИС становится уделом единичных избранных мировых компаний.

- 9. Гигантские расходы на разработку и производство современных сверхсложных интегральных микросхем, способные разорить военный бюджет даже богатых государств, вынудят пользователей из военной сферы ускорить давно сформировавшуюся мировую тенденцию по максимальному использованию в своих изделиях гражданской продукции, технологий и чипов, систем-на-кристалле, многокристалльных и 2,5-3D-сборок. Это приведет к стиранию граней между гражданской, военной продукцией, изделиями двойного применения и еще больше усложнит к ним доступ стран, находящихся под санкциями.

- 10. Гонка инвестиций мировых лидеров TSMC и Samsung на американской территории с планами строительства в США фабрик по технологиям 5 и 3 нм пойдет на пользу американской полупроводниковой промышленности, что можно считать бескровной победой американской администрации.

■

## ЛИТЕРАТУРА

- 1. IBM and Intel both announce high-k gate dielectric transistors. Semiconductor Today. January 30. 2007//www.semiconductor-today. com.

- 2. FinFET Transistor Technology. Electronics Notes//www.electronics-notes.com.

- 3. Intel 22nm 3-D Tri-Gate Transistor Technology. Intel Press Kit. May 2. 2011//www.intel.com.

- 4. Радиус атома, справочная таблица. Формулы и расчеты online//www.fxyz.ru.

- 5. Передовые 5-нм и 7-нм производства TSMC полностью загружены

- до второй половины 2021 года. 3DNews. 16.11.2020//www.3dnews.ru.

- 6. TSMC Showcases Leading Technologies at Online Technology Symposium and OIP Ecosystem Forum. TSMC News. August 25. 2020//www.tsmc.com.

- 7. TSMC Details 3nm Process Technology: Full Node Scaling for 2H22 Volume Production. AnandTech. August 24. 2020//www.anandtech.

- 8. TSMC Showcases Leading Technologies at Online Technology Symposium and OIP Ecosystem Forum. GizChina. September 23. 2020//www.qizchina.com.

- 9. Samsung May Take-Over Apple M1 Chip Production. GizChina. November 13. 2020//www. aizchina.com.

- 10. Соперничество с TSMC вынудило Samsung инвестировать в производство чипов астрономические 116 млрд долл. Время электроники. 18 ноября 2020//www.russianelectronics.ru.

- 11. Samsung Makes the First 3nm GAAFET Semiconductor. WCCFTECH. January 4. 2020//www.wccftech.com.

- 12. Samsung Intensifies Chip Wars with Bet It Can Catch TSMC by 2022. Bloomberg. November 17, 2020//www.bloomberg.com.

- 13. IMEC Presents Forksheet Device as the Ultimate Solution to Push Scaling Towards the 2nm Technology Node. IMEC. December 9. 2019//www.imec.com.

- 14. IMEC Reports Breakthrough in Extending Interconnects Beyond the 3 nm Technology Node. IMEC. July 9. 2018//www.imec.com.

- 15. Intel's Manufacturing Roadmap from 2019 to 2029: Back Porting, 7nm, 5nm, 3nm, 2nm, and 1.4 nm. AnandTech. December 11. 2019//www.anandtech.com.

- 16. International Roadmap for Devices and Systems 2020 Update More Moore. IEEE 2020//www.irds.ieee.org.

- 17. 5/3nm Wars Begin. Semiconductor Engineering. January 23. 2020//www.semiengineering.com.

- 18. Big Trouble At 3nm. Semiconductor Engineering. June 21. 2018//www.semiengineering.com.

- 19. EUV lithography revisited. LaserFocusWorld. August 29. 2019//www.laserfocusworld.com.

- 20. EUV Lithography Systems Twinscan NXE 3400B, Twinscan NXE 3400C//www.asml.com.

- 21. ASML to Ship 30 EUV Scanners in 2019: Faster EUV Tools Coming. AnandTech. January 28. 2019//www.anandtech.com.

- 22. Al Chips: What They Are and Why They Matter. Center for Security and Emerging Technology. April 2020//www.cset.com.

- 23. Apple A13 & Beyond How Transistor Count and Costs Will Go Up. WCCFTECH. April 19. 2019//www.wccftech.com.

- 24. TSMC, Manufacturing Excellence. TSMC Technology Symposium 2020. August 25. 2020.